- 机器人、自动化、工业信息技术 >

- 工业软件 >

- CAD软件 >

- SIEMENS/西门子

SIEMENS/西门子CAD软件

{{product.productLabel}} {{product.model}}

{{#if product.featureValues}}{{product.productPrice.formattedPrice}} {{#if product.productPrice.priceType === "PRICE_RANGE" }} - {{product.productPrice.formattedPriceMax}} {{/if}}

{{#each product.specData:i}}

{{name}}: {{value}}

{{#i!=(product.specData.length-1)}}

{{/end}}

{{/each}}

{{{product.idpText}}}

{{product.productLabel}} {{product.model}}

{{#if product.featureValues}}{{product.productPrice.formattedPrice}} {{#if product.productPrice.priceType === "PRICE_RANGE" }} - {{product.productPrice.formattedPriceMax}} {{/if}}

{{#each product.specData:i}}

{{name}}: {{value}}

{{#i!=(product.specData.length-1)}}

{{/end}}

{{/each}}

{{{product.idpText}}}

... ReqTracer 在设计规格和需求之间架起了一座桥梁,从而提高了传统(定向测试)和高级验证的生产率和有效性。 ReqTracer 确定设计要求是否得到满足,意味着您可以跟踪从规格到 RTL 描述再到验证结果的整个过程--这是任何基于要求的设计流程的最佳实践。ReqTracer 可让您轻松实施和跟踪需求驱动型项目开发流程。 ...

Siemens EDA/西门子

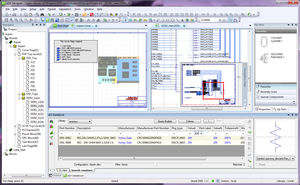

... Xpedition EDM数据管理工具套件旨在为整个企业的工程和外部PLM和ERP系统之间提供无缝集成。这种集成利用企业数据交换(EDX)数据格式,在整个产品生命周期中共享数据。EDX在一个包中捕获并保护你的EDA数据,以实现安全的数据交换和简化的流程集成。EDX实现了一个独立于版本和内部工具数据库结构的强大而稳定的接口。 ...

Siemens EDA/西门子

... 为什么印刷电路板(PCB)设计的重新设计是意料之中而非例外情况?根据历史数据,进度表和预算通常包括数次重新设计。集成到 Xpedition 软件中的 Valor NPI 软件已证明,利用可制造性设计 (DFM) 技术,可将重新设计的次数平均减少 57%,从而在流程早期发现并纠正制造问题,节省资金和时间。 DFM 分析的优势 通过及早发现和纠正问题,节省时间和金钱 提供无缝、并发的 ...

Siemens EDA/西门子

功能强大的设计空间探索和优化软件,可与 CAD 和 CAE 工具连接,推动产品创新。 HEEDS 通过自动化分析工作流程、实现可用计算硬件和软件资源的高效利用、高效探索创新解决方案的设计空间,同时评估新概念以确保满足性能要求,从而加速产品开发过程。 实现流程自动化 HEEDS 支持工作流程自动化,以便轻松推动产品开发流程。HEEDS 拥有丰富的商业计算机辅助设计 ...

Siemens EDA/西门子

... Oasys-RTL 通过在更高的抽象层次上进行优化,并使用集成的平面规划和布局功能,满足了对更高容量、更快运行时间、更好的 QoR 和物理感知的需求。 快速、高质量的物理 RTL 合成 Oasys-RTL 通过实现物理精度、底层规划和快速优化迭代来提高结果质量,从而按时完成设计。 功率感知合成 功率感知综合功能包括支持多阈值库、自动时钟门控和基于 UPF 的多VDD 流程。在综合过程中,Oasys-RTL 会根据 UPF 中定义的功耗意图,插入所有适当的电平转换器、隔离单元和保持寄存器。 直接从 ...

Siemens EDA/西门子

... 基于标准、OpenAccess、iPDK 和 TCL 的模拟混合信号设计的定制 IC 原理图驱动布局。 定制集成电路布局 L-Edit 是一款完整的分层物理布局编辑器,可在处理最复杂布局的同时提高工作效率。L-Edit 支持定制和原理图驱动布局。 处理最复杂的全定制设计 完全自定义分层物理布局 支持 FinFET、平面和所有其他晶体管技术 为功率晶体管、MEMS 和光子学提供内置的全角度和曲线支持 支持多用户的本地 OpenAccess ...

Siemens EDA/西门子

... 在先进工艺节点上进行设计,需要一种新的布局布线范式来管理日益增加的复杂性。Aprisa 是面向现代 SoC 的以细节路由为中心的物理设计平台。 适用于复杂 SoC 设计的布局布线技术 Aprisa 为复杂的数字集成电路设计提供顶层分层设计和块级实现的完整功能。以细节布线为中心的架构和分层数据库可快速完成设计,并以极具竞争力的运行时间实现最佳的结果质量。 减少迭代 以详细路由为中心的架构 实现布局优化、CTS 优化和详细路由之间的高效通信,从而提高结果质量,减少迭代次数,并将设计收敛速度提高 ...

Siemens EDA/西门子

... 由于设计规模更大、更复杂、错误数量更多以及验证迭代次数更多,总周期时间不断增加。Calibre nmDRC 平台通过创新功能满足了缩短周期时间的需求,使 Calibre nmDRC 技术有别于传统的 DRC 工具。 业界领先的签收设计规则检查 Calibre nmDRC 平台凭借其不断创新的功能,满足最复杂的规则需求,以及业界领先的性能和容量,25 年来一直被所有主要代工厂采用为内部签收 DRC 解决方案。 首选代工厂签核工具 Calibre nmDRC ...

Siemens EDA/西门子

... 将物理验证从集成电路领域扩展到高级封装领域,提高多芯片封装的可制造性。使用一个 Calibre 驾驶舱进行装配级 DRC、LVS 和 PEX,而无需中断传统的封装格式和工具。 多芯片、系统级对齐/连接性检查 Calibre 3DSTACK 工具扩展了 Calibre 裸片级签核验证,可完成各种 2.5D 和 3D 堆叠裸片设计的签核验证。设计人员可以使用现有的工具流程和数据格式,在任何工艺节点上对完整的多芯片系统进行签核 DRC 和 LVS 检查。 多芯片/芯片封装/叠片对齐检查 Calibre ...

Siemens EDA/西门子

... 经代工厂认证,AFS 平台的 nm SPICE 精确度比传统 SPICE 快 5 倍以上,比并行 SPICE 仿真器快 2 倍以上。为模拟、射频、混合信号和定制数字电路提供最快的 nm 电路验证平台。现在包括新的 eXTreme 技术。 主要功能 模拟快速 SPICE 平台 AFS 具有代工厂认证的精度,其纳米 SPICE 精度比传统 SPICE 快 5 倍以上,比并行 SPICE 仿真器快 2 倍以上。对于大型布局后电路,全新的 AFS eXTreme 技术可提供超过 ...

Siemens EDA/西门子

为提升搜索质量,您认为我们应改善:

请说明:

您的建议是我们进步的动力:

剩余字数