- 机器人、自动化、工业信息技术

- 工业软件

- 设计软件

- Siemens EDA/西门子

设计软件 Calibre 3DSTACK验证连接性流程

添加到我的收藏夹

添加到产品对比表

产品规格型号

- 功能

- 设计, 验证, 连接性

- 应用

- 流程, 对齐

- 类型

- 3D

产品介绍

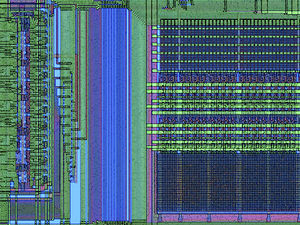

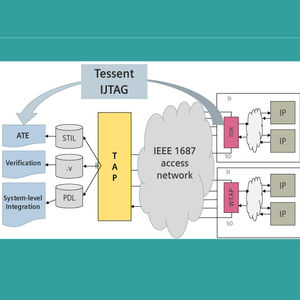

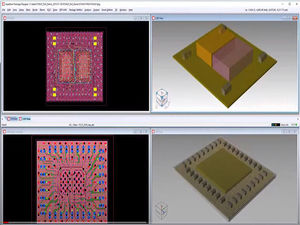

将物理验证从集成电路领域扩展到高级封装领域,提高多芯片封装的可制造性。使用一个 Calibre 驾驶舱进行装配级 DRC、LVS 和 PEX,而无需中断传统的封装格式和工具。

多芯片、系统级对齐/连接性检查

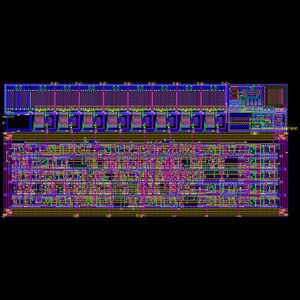

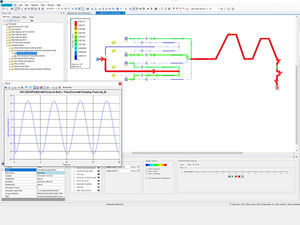

Calibre 3DSTACK 工具扩展了 Calibre 裸片级签核验证,可完成各种 2.5D 和 3D 堆叠裸片设计的签核验证。设计人员可以使用现有的工具流程和数据格式,在任何工艺节点上对完整的多芯片系统进行签核 DRC 和 LVS 检查。

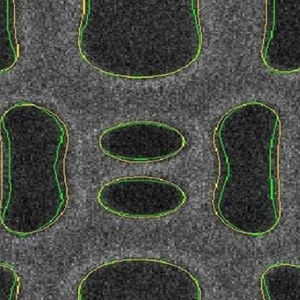

多芯片/芯片封装/叠片对齐检查

Calibre 3DSTACK 工具使设计人员能够检查多芯片封装组件中不同芯片之间的精确对准。

多芯片、系统级连接性检查

Calibre 3DSTACK 工具支持多裸片封装组件的系统级连接性检查,使设计人员能够验证裸片、中间件和封装是否按预期连接。

中间件/封装连接性检查

Calibre 3DSTACK 工具使设计人员能够检查独立的中间件/封装连接性,而无需包括单个裸片设计数据库。

---

PDF产品目录

该产品还没有PDF产品手册

查看Siemens EDA的所有产品目录